# Exploration d'architectures génériques sur FPGA pour des algorithmes d'imagerie multispectrale

Junyan Tan

# ▶ To cite this version:

Junyan Tan. Exploration d'architectures génériques sur FPGA pour des algorithmes d'imagerie multispectrale. Autre [cond-mat.other]. Université Jean Monnet - Saint-Etienne, 2012. Français. NNT: 2012STET4028. tel-00838037v2

# HAL Id: tel-00838037 https://theses.hal.science/tel-00838037v2

Submitted on 29 Apr 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Rhône Alpes

# **THESE**

Présentée par

# **Junyan TAN**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITE JEAN MONNET

Discipline: microélectronique

Laboratoire Hubert Curien UMR CNRS 5516

Département Informatique Image

# Exploration d'architectures génériques sur FPGA pour des algorithmes d'imagerie multispectrale

Soutenance le 12 Juin 2012 devant la commission d'examen

# **JURY**

| M. Frédéric Rousseau    | Professeur TIMA-UJF            | Directeur de thèse     |

|-------------------------|--------------------------------|------------------------|

| Mme. Virginie Fresse    | Maitre de Conférences LaHC-UJM | Co-directrice de thèse |

| M. Yves Ledru           | Professeur LIG-UJF             | Président              |

| M. El-Bay Bourennane    | Professeur LE2I-Dijon UB       | Rapporteur             |

| M. Mohamed Akil         | Professeur ESIEE               | Rapporteur             |

| M. Fernando Gehm Moraes | Professeur PUC-Brésil          | Examinateur            |

| M. Érik Hochapfel       | Fondateur/IngénieurADACSYS     | Examinateur            |

# Remerciements

Aucun travail ne s'accomplit dans la solitude.

J'ai tout au long de mon doctorat eu le soutien de plusieurs personnes et je tiens à leur exprimer ma gratitude.

Tout d'abord j'aimerais remercier mes deux directeurs de thèse qui m'ont encadrée pendant ces années et sans qui ce travail n'aurait pas pu se faire : monsieur Frédéric Rousseau et madame Virginie Fresse. Ils se sont montrés disponibles, attentifs, ont toujours su orienter mon travail et m'ont prodigué des conseils avisés.

J'aimerais également remercier les membres du jury qui ont accepté de prendre de leur temps pour valider mes travaux et plus particulièrement monsieur El-Bay Bourennane et monsieur Mohamed Akil qui m'ont fait l'honneur d'assumer le rôle difficile de rapporteur.

Je tiens à remercier tous mes collègues du groupe System-Level-Synthesis au laboratoire TIMA à Grenoble, et du groupe Image Processing au laboratoire Hubert Curien à Saint Etienne.

De plus j'aimerais remercier la région Rhône-Alpes pour m'avoir accordé le financement de ses recherches.

Pour terminer, je remercie chaleureusement mes parents, mon mari, mes grands parents, mes amis pour m'avoir soutenue dans les bons et moins bons moments et pour m'avoir donné l'envie d'apprendre.

# Résumé

Les architectures multiprocesseur sur puce (MPSoC) basées sur les réseaux sur puce (NoC) constituent une des solutions les plus appropriées pour les applications embarquées temps réel de traitement du signal et de l'image. De part l'augmentation constante de la complexité de ces algorithmes et du type et de la taille des données manipulées, des architectures MPSoC sont nécessaires pour répondre aux contraintes de performance et de portabilité. Mais l'exploration de l'espace de conception de telles architectures devient très coûteuse en temps. En effet, il faut définir principalement le type et le nombre des cœurs de calcul, l'architecture mémoire et le réseau de communication entre tous ces composants. La validation par simulation de haut niveau manque de précision, et la simulation de bas niveau est inadaptée au vu de la taille de l'architecture. L'émulation sur FPGA devient donc inévitable.

Dans le domaine de l'image, l'imagerie spectrale est de plus en plus utilisée car elle permet de multiplier les intervalles spectraux, améliorant la définition de la lumière d'une scène pour permettre un accès à des caractéristiques non visibles à l'œil nu. De nombreux paramètres modifient les caractéristiques de l'algorithme, ce qui influence l'architecture finale.

L'objectif de cette thèse est de proposer une méthode pour dimensionner au plus juste l'architecture matérielle et logicielle d'une application d'imagerie multispectrale. La première étape est le dimensionnement du NoC en fonction du trafic sur le réseau. Le développement automatique d'une plateforme d'émulation sur mono ou multi FPGA facilite cette étape et détermine le positionnement des composants de calcul. Ensuite, le dimensionnement des composants de calcul et leurs fonctionnalités sont validés à l'aide de plateformes de simulation existantes, avant la génération du modèle synthétisable sur FPGA. Le flot de conception est ouvert dans le sens qu'il accepte différents NoC à condition d'avoir le modèle source HDL de ce composant.

De nombreux résultats mettent en avant les paramètres importants qui ont une influence sur les performances des architectures et du NoC en particulier. Plusieurs solutions sont décrites, commentées et critiquées. Ces travaux nous permettent de poser les premiers jalons d'une plateforme d'émulation complète MPSoC à base de NoC.

# **Abstract**

The Multiprocessor-System-On-Chip (MPSoC) architectures based on the Network-On-Chip (NoC) communication are the one of the most appropriate solution for image and signal processing applications under real time constraints. Due to the ever increasing complexity of these algorithms, the types and sizes of the data manipulated, the MPSoC architectures are necessary to meet the constraints of performance and portability. However exploring the design space of such architecture is time consuming. Indeed, many parameters should be defined such as the type and the number of processing cores, the memory architecture and the communication network between all these components. Validation by high-level simulations has the lack of the precision. Low-level simulation is inadequate for such big size of the architecture. Therefore, the emulation on FPGA becomes inevitable.

In image processing, spectral imaging is more and more used. This technology captures light from more frequencies than the human eye increasing the number of wavelengths. Invisible details can be extracted from a scene. The difference between all spectral imaging applications is the number of wavelengths and the precision. Many parameters affect the characteristics of the algorithm, having a huge impact on the final architecture.

The objective of this thesis is to propose a method for sizing one of the most accurate hardware and software architecture for multispectral imaging application. The first step is the design of the NoC based on the network traffic. The automatic development of an emulation platform on a single FPGA or multi-FPGAs simplifies this step and determines the positioning of the computational components. Then, the design of computational components and their functions are validated using existing simulation platforms. The synthesizable model of the architecture on FPGA is then generated. The design flow is open. Several NoC structures can be inserted using the source model of this component.

The set of results obtained points out the major parameters influencing the performances of architecture and the NoC itself. Several solutions are described and analyzed. These studies allow us to lay the groundwork for a complete MPSoC emulation platform based on NoC.

# **Sommaire**

| Liste des Figures                                                                                    | 2  |

|------------------------------------------------------------------------------------------------------|----|

| Liste des Tableaux                                                                                   | 7  |

| Glossaire                                                                                            | 8  |

| Chapitre 1. Introduction                                                                             | 9  |

| 1.1 Contribution                                                                                     | 11 |

| 1.2 Plan du manuscrit                                                                                | 11 |

| 1.2.1 Applications et principes de base des architectures                                            | 12 |

| 1.2.2 Proposition d'une méthodologie pour la conception et l'exploration de NoC                      | 12 |

| 1.2.3 Implémentation et évaluation des NoC pour l'évaluation et l'exploration l'espace de conception |    |

| 1.2.4 Expérimentation : Implantation d'algorithmes d'imagerie multi-spectrale                        | 13 |

| Chapitre 2. Applications et principe de base des architectures                                       | 14 |

| 2.1 Imagerie couleur et multispectrale                                                               | 14 |

| 2.1.1 Imagerie couleur                                                                               | 14 |

| 2.1.2 Imagerie Multispectrale                                                                        | 18 |

| 2.2 Processus d'authentification en Imagerie Multispectrale                                          | 18 |

| 2.2.1 Principe de l'algorithme d'authentification pour les œuvres d'arts                             | 19 |

| 2.2.2 Calculs de distance dans des espaces couleurs                                                  | 21 |

| 2.2.3 Calculs de distance dans l'espace spectral                                                     | 21 |

| 2.2.4 Conclusion                                                                                     | 22 |

| 2.3 Les architectures programmables embarquées pour l'algorithme d'authentification                  | 23 |

| 2.3.1 Processeur généraliste dans l'embarqué : AMD Athlon 64                                         | 23 |

| 2.3.2 Processeur spécialisé : GPU                                                                    | 23 |

| 2.4 Performances sur CPU et GPU                                                                      | 26 |

| 2.4.1         | Exécutions sur CPU                                                        | 26 |

|---------------|---------------------------------------------------------------------------|----|

| 2.4.2         | Exécutions sur GPU (Graphics Processing Unit)                             | 27 |

| 2.4.3         | Analyse des temps d'exécution sur architecture CPU et GPU                 | 31 |

| 2.5 Les       | réseaux de communication sur puces                                        | 32 |

| 2.5.1         | Le réseau sur puce (NoC)                                                  | 32 |

| 2.5.2         | Les NoCs sur FPGA                                                         | 38 |

| 2.6 Co        | nclusion                                                                  | 40 |

| Chapitre 3. I | Proposition d'une méthodologie pour la conception et l'exploration de NoC | 41 |

| 3.1 Arc       | chitectures NoC et plateformes d'évaluation                               | 41 |

| 3.1.1         | Les NoC sur FPGA                                                          | 41 |

| 3.1.2         | Les plateformes d'évaluation et d'émulation de NoC                        | 43 |

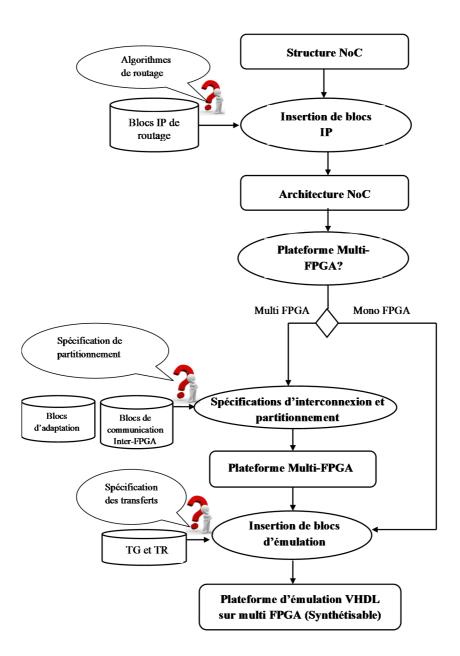

|               | thodologie pour la conception et l'exploration de NoC : proposition d'un  |    |

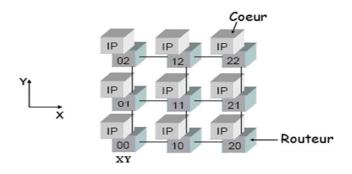

| 3.2.1         | Structure de NoC                                                          | 45 |

| 3.2.2         | Algorithme de routage                                                     | 47 |

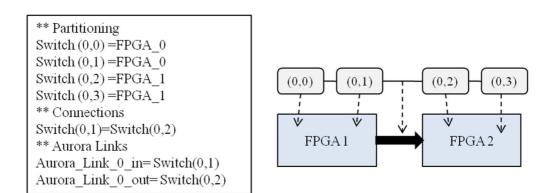

| 3.2.3         | Blocs d'adaptation pour la communication inter-FPGA                       | 48 |

| 3.2.4         | Blocs d'émulation                                                         | 49 |

| 3.2.5         | Spécification des transferts de données                                   | 52 |

| 3.2.6         | Spécification de partitionnement                                          | 54 |

| 3.2.7         | Flot de conception                                                        | 56 |

| 3.3 Eva       | aluation des performances                                                 | 58 |

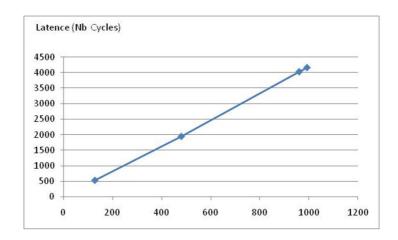

| 3.3.1         | Latence                                                                   | 58 |

| 3.3.2         | Mesure du débit                                                           | 59 |

| 3.4 Co        | nclusion                                                                  | 59 |

| Chapitre 4. I | mplémentations et évaluation des performances des NoCs                    | 60 |

| 4.1 Le        | NoC Hermes                                                                | 60 |

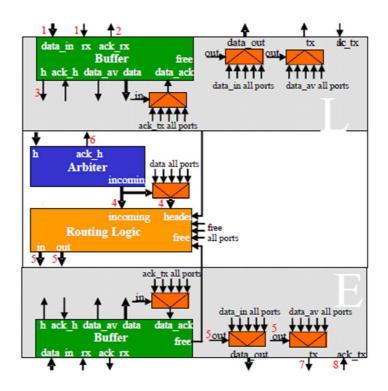

| 4.1.1         | Structure du NoC Hermes                                                   | 60 |

| 4.1.2         | L'interface graphique pour la génération du NoC : ATLAS                   | 63 |

| 4.2 Objectifs et outils pour l'évaluation et l'exploration                                                               |

|--------------------------------------------------------------------------------------------------------------------------|

| 4.2.1 L'interface graphique NoCGen                                                                                       |

| 4.2.2 Les architectures Xilinx et les outils associés                                                                    |

| 4.3 Etude des performances sur mono-FPGA                                                                                 |

| 4.3.1 Exploration du nombre de nœuds                                                                                     |

| 4.3.2 Impact des blocs d'émulation                                                                                       |

| 4.3.3 Exploration de la taille des paquets, des flits et du nombre de blocs d'émulation 68                               |

| 4.3.4 Exploration des différents algorithmes de routage et du placement des blocs d'émulation                            |

| 4.4 Etude des performances du NoC sur multi-FPGA                                                                         |

| 4.4.1 Evaluation temporelle                                                                                              |

| 4.5 Analyse des résultats pour le dimensionnement du NoC                                                                 |

| 4.6 Conclusion 88                                                                                                        |

| Chapitre 5. Expérimentation : Implantation d'algorithmes d'imagerie multi-spectrale sur une architecture multiprocesseur |

| 5.1 Différents plateformes de génération et simulation de MPSoC                                                          |

| 5.1.1 SocLib                                                                                                             |

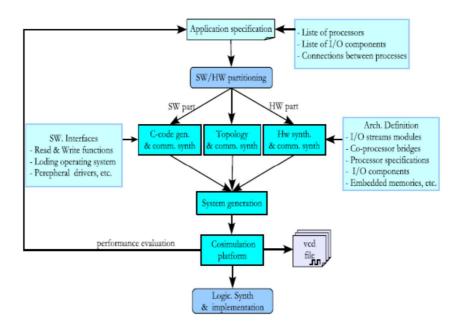

| 5.1.2 STARSoC                                                                                                            |

| 5.1.3 SESAM                                                                                                              |

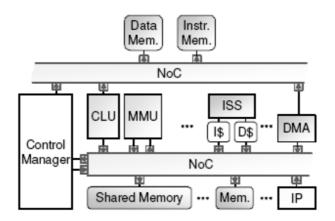

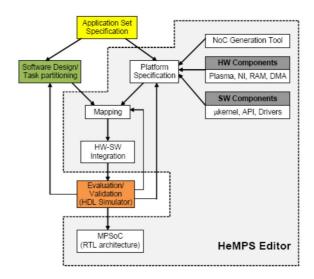

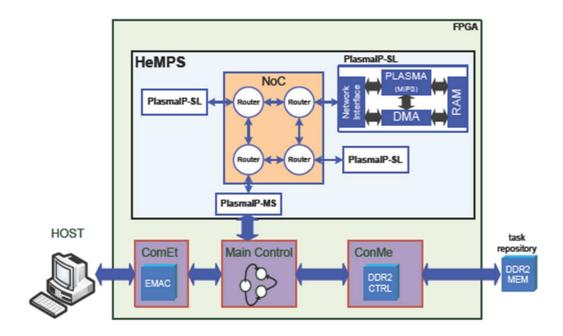

| 5.1.4 La plateforme HeMPS                                                                                                |

| 5.2 Expérimentation de l'architecture MPSoC pour l'application                                                           |

| 5.2.1 L'architecture HeMPS                                                                                               |

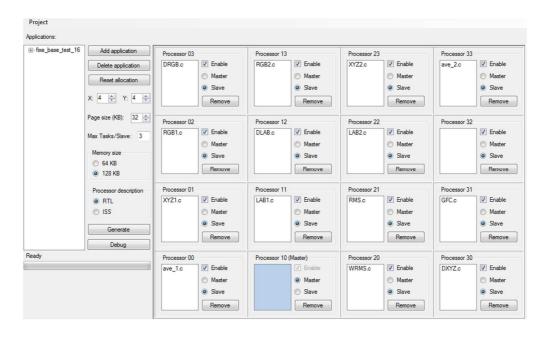

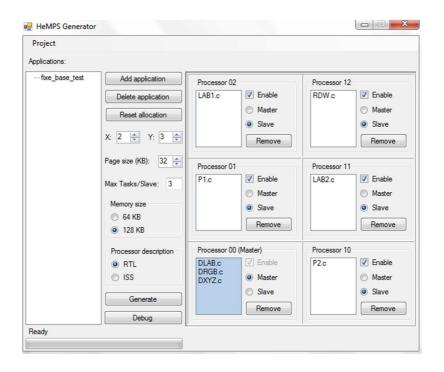

| 5.2.2 L'outil de génération HeMPS                                                                                        |

| 5.2.3 Etude de performances de l'architecture HeMPS pour l'application d'authentification d'œuvre d'art                  |

| 5.2.4 Expérimentations sur une architecture MPSoC de taille 2x3                                                          |

| 5.2.5 Implantation de la plateforme d'émulation HeMPS MPSoC sur FPGA 106                                                 |

| 5.3 Analyse des expérimentations                                                                                         |

| 5.4 Analyse des résultats                                                                                                |

| Chapitre 6.  | Conclusions et perspectives | 110 |

|--------------|-----------------------------|-----|

| 6.1          | Conclusion                  | 110 |

| 6.2          | Perspectives                | 111 |

|              |                             |     |

| Liste des Pu | ublications                 | 114 |

| Bibliograph  | nie                         | 115 |

# **Prologue**

Les travaux de recherche menés et présentés dans ce manuscrit ont été effectués dans le cadre d'une bourse région Rhône-Alpes, projet Semba (Systèmes Embarqués). Cette thèse est faite en collaboration entre le laboratoire Hubert Curien Saint Étienne, équipe Image Processing, unité mixte de recherche CNRS 5516 de l'université Jean Monnet, et le laboratoire Technique de l'Informatique et de la Microélectronique pour l'Architecture d'ordinateurs (TIMA) Grenoble, équipe System Level Synthesis (SLS), unité mixte de recherche CNRS 5159, de Grenoble INP (Institut Polytechnique de Grenoble) et de l'Université Joseph Fourier.

# Liste des Figures

| Figure 1-1 : Loi de Moore/ More than Moore : miniaturisation des fonctions numériques condiversification fonctionnelle.      |      |

|------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2-1 : Le cube de couleurs RGB [11]                                                                                    | . 15 |

| Figure 2-2 : Les fonctions colorimétriques $X(\lambda),\ Y(\lambda)$ et $Z(\lambda)$                                         | . 16 |

| Figure 2-3 : Modèle de représentation dans l'espace couleur L*a*b* [14]                                                      | . 17 |

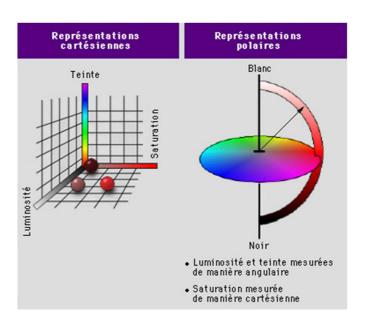

| Figure 2-4 : Représentations cartésiennes et polaires [14]                                                                   | . 17 |

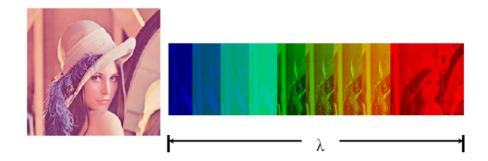

| Figure 2-5: Imagerie multispectrale.                                                                                         | . 18 |

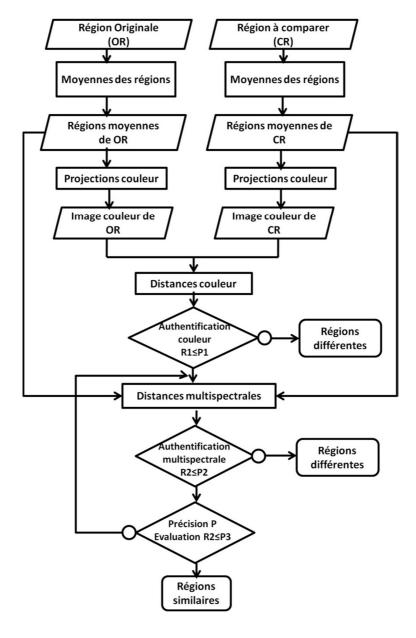

| Figure 2-6 : Processus d'authentification d'œuvres d'art en imagerie spectrale.                                              | . 20 |

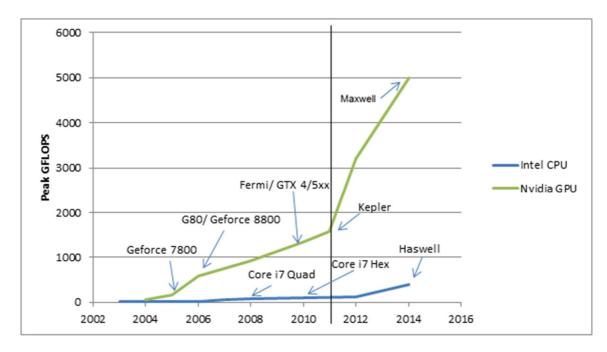

| Figure 2-7 : Evolution de processeurs généralistes / GPU[20]                                                                 | . 24 |

| Figure 2-8 : Architecture GPU NVIDIA Geforce [22]                                                                            | . 25 |

| Figure 2-9 : Stratégie des architectures CPU et GPU.                                                                         | . 26 |

| Figure 2-10 : Algorithme d'authentification parallélisé sur une architecture GPU à processeurs par MP.                       |      |

| Figure 2-11 : Temps de traitement, d'accès mémoire et temps d'exécution total                                                | . 29 |

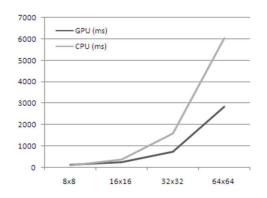

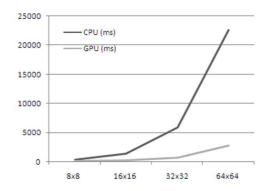

| Figure 2-12 : Pourcentage d'occupation du GPU entre le calcul et le transfert                                                | . 30 |

| Figure 2-13 : Calcul du temps d'exécution en fonction du nombre de régions (taille de fende 64*64 pour 992 longueurs d'onde) |      |

| Figure 2-14 : Temps d'exécution de l'application sur CPU et GPU pour W=128                                                   | . 31 |

| Figure 2-15 : Temps d'exécution de l'application sur CPU et GPU pour W=480                                                   | . 31 |

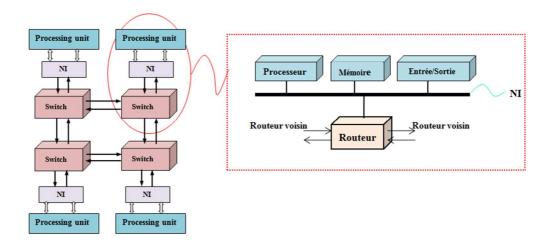

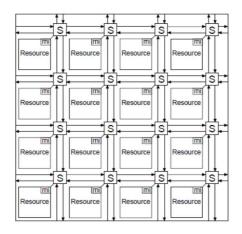

| Figure 2-16 : Architecture de NoC                                                                                            | . 33 |

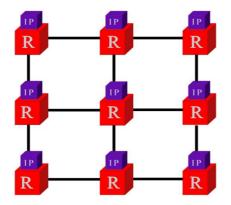

| Figure 2-17 : Topologie 2D maillée                                                                                           | . 34 |

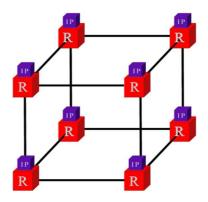

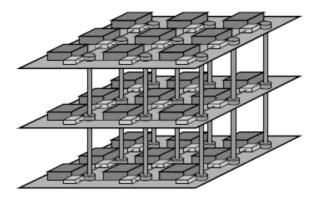

| Figure 2-18 : Topologie 3D maillée                                                                                           | . 34 |

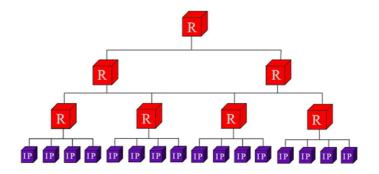

| Figure 2-19 : Topologie en arbre élargie (fat-tree)                                                                          | . 35 |

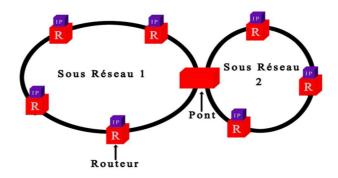

| Figure 2-20 : Topologie en anneau                                                                                            | . 35 |

| Figure 2-21 : Réseau hybride avec topologie en anneaux hiérarchiques                                                                                                                                                                                            | 35    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

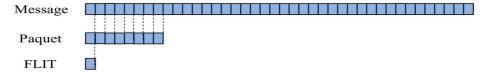

| Figure 2-22 : Format des données circulant dans un NoC                                                                                                                                                                                                          | 36    |

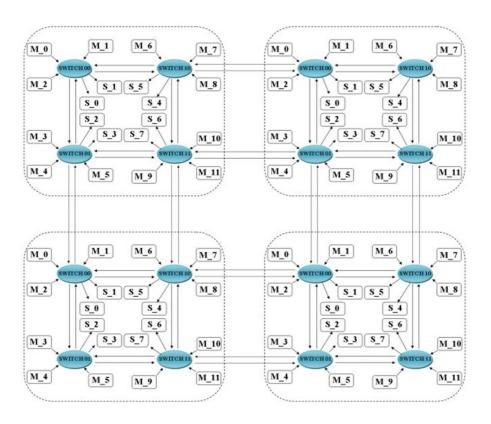

| Figure 3-1 : Déploiement du NoC sur 4 FPGAs                                                                                                                                                                                                                     | 42    |

| Figure 3-2 :Structure de NoC dédiée aux architectures multi-composant. Des blocs dédiés communications inter-composant sont conçus et intégrés dans la structure du NoC [74]                                                                                    |       |

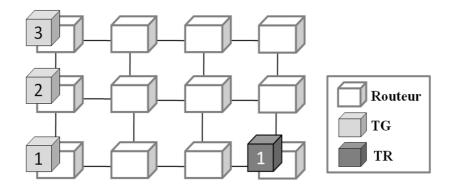

| Figure 3-3 : Structure de NoC intégrée au flot de conception.                                                                                                                                                                                                   | 46    |

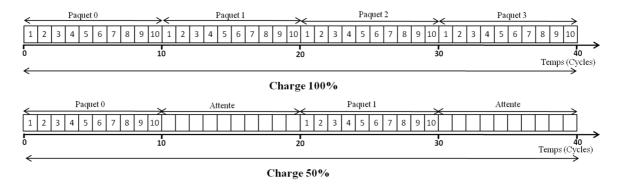

| Figure 3-4 : Exemples de charge de réseau : 100% pour une charge continue du réseau et :                                                                                                                                                                        |       |

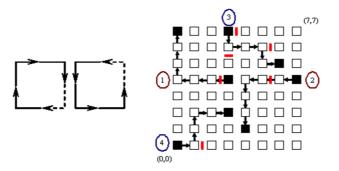

| Figure 3-5 : Algorithme de routage West First. Les routages du chemin 1 et 2 sont déterminalors que les chemins 3 et 4 utilisent un routage adaptatif. Les tours sud-ouest et nord-es sont pas autorisés.                                                       | st ne |

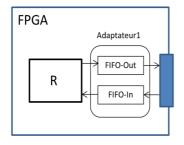

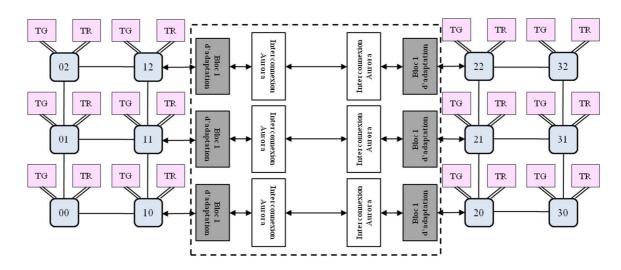

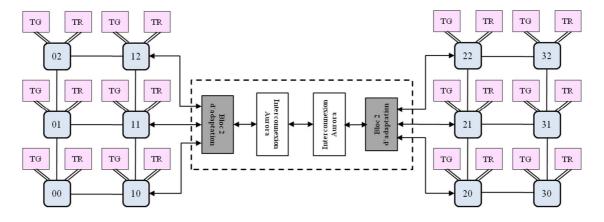

| Figure 3-6: Blocs d'adaptation pour une communication routeur-routeur                                                                                                                                                                                           | 49    |

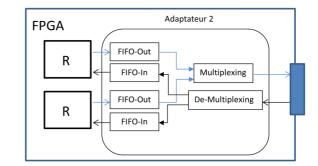

| Figure 3-7: Blocs d'adaptation pour une communication multi-routeurs                                                                                                                                                                                            | 49    |

| Figure 3-8 : Format des paquets générés par le TG pour une émulation mono-FPGA                                                                                                                                                                                  | 50    |

| Figure 3-9 : Format des paquets générés par le TG pour une émulation multi-FPGA                                                                                                                                                                                 | 50    |

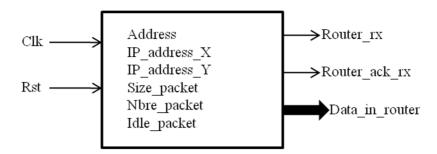

| Figure 3-10 : Signaux et paramètres pour les générateurs de trafic génériques                                                                                                                                                                                   | 51    |

| Figure 3-11 : Spécification de transferts de données de plusieurs initiateurs vers plusi<br>destinataires avec des charges de réseau fixe.                                                                                                                      |       |

| Figure 3-12 : Spécification de transferts de données d'un initiateur vers plusieurs destinata avec une variation automatique de la charge du réseau.                                                                                                            |       |

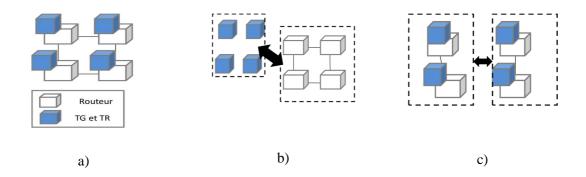

| Figure 3-13 : Solutions de partitionnement d'un NoC maillé. A partir d'un NoC original (a) l'ère solution consiste à séparer le NoC des nœuds (b) alors que la 2 <sup>ème</sup> solution consiste à co le NoC en gardant chaque nœud associé à son routeur (c). | upei  |

| Figure 3-14 : Partitionnement d'un NoC 4x1 sur deux FPGAs. Le package contien placement des routeurs sur les FPGAs, indique les routeurs connectés via un ou plusieurs l'externes ainsi que le sens des communications externes.                                | liens |

| Figure 3-15 : Flot de conception pour la génération de la plateforme d'émulation sur FPGA.                                                                                                                                                                      | 56    |

| Figure 3-16 : Exemple de sélection d'algorithme de routage dans le package routage                                                                                                                                                                              | 57    |

| Figure 4-1 : Topologie maillée 2D du NoC Hermes.                                                                                                                                                                                                                | 61    |

| Figure 4-2 : Structure du routeur Hermes. Chaque entrée contient un buffer pou mémorisation des paquets. Un bloc de routage et d'arbitrage transfère des paquets vers le correspondant                                                                          | lier  |

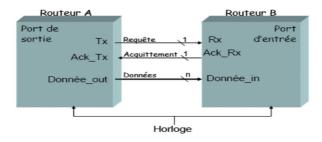

| Figure 4-3 : Structure de communication entre deux routeurs en mode « handshake »                                                                                                                                                                               | 62    |

| Figure 4-4 : Structure de communication entre deux routeurs en mode « credit-based » 62                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

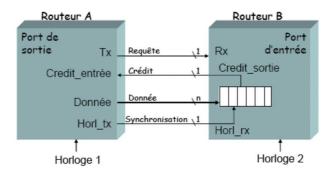

| Figure 4-5 : Le logiciel ATLAS. A gauche, l'utilisateur définit les paramètres du NoC et choisit ou non de générer le testbench en SystemC. A droite, la vue du NoC généré |

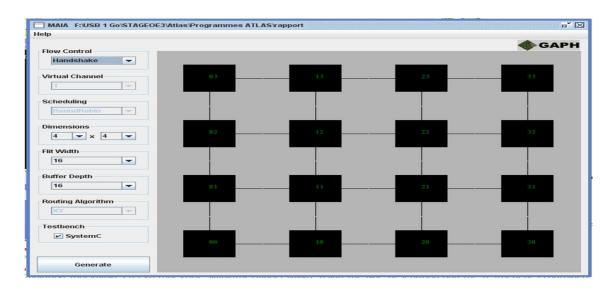

| Figure 4-6 : Interface graphique NoCGen développée autour du flot de conception                                                                                            |

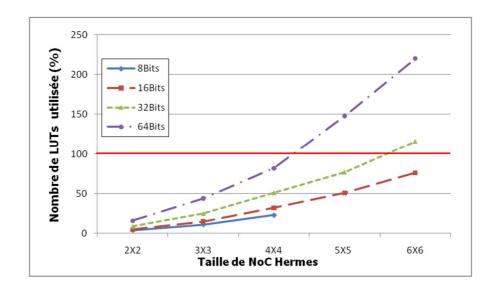

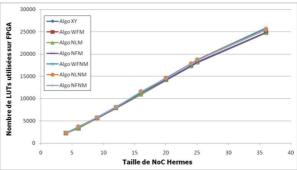

| Figure 4-7 : Nombre de LUTs utilisées sur Xilinx Virtex 5 pour différentes tailles du NoC Hermes                                                                           |

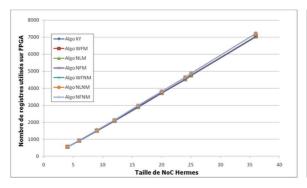

| Figure 4-8 : Nombre de registres utilisés par Hermes sur Xilinx Virtex 5 pour différentes tailles de NoC                                                                   |

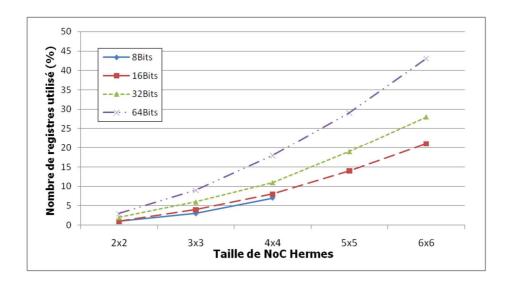

| Figure 4-9: Nombres de ressources pour un NoC 4x2 sans blocs d'émulation et avec blocs d'émulation en fonction de la taille des flits                                      |

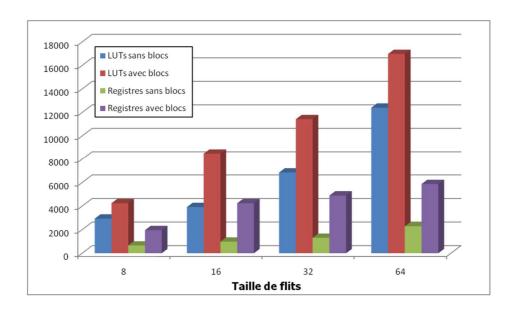

| Figure 4-10 : Deux scénarii utilisés pour l'exploration de paramètres du NoC (scénario 1 à gauche et scénario 2 à droite).                                                 |

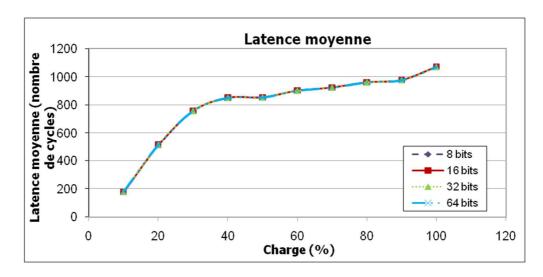

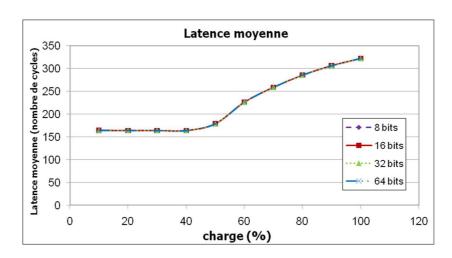

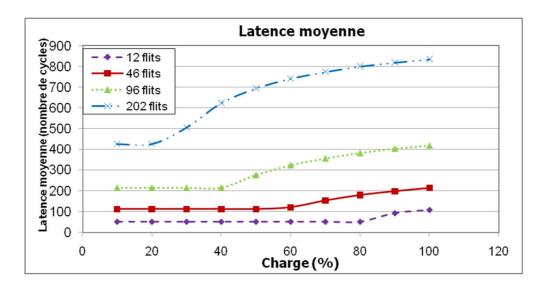

| Figure 4-11 : Latence moyenne pour le scénario 1 sur le NoC 3x3 pour différentes charges 69                                                                                |

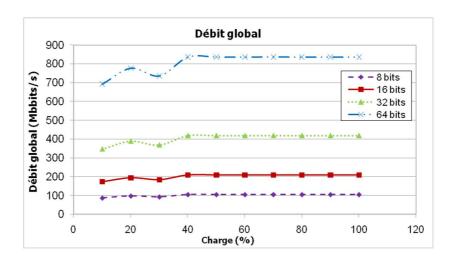

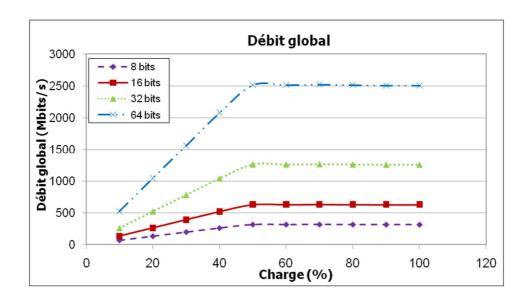

| Figure 4-12 : Débit global pour le scénario 1 sur le NoC 3x3 pour différentes charges70                                                                                    |

| Figure 4-13 : Latence moyenne pour le scénario 2 sur le NoC 3x3 pour différentes charges70                                                                                 |

| Figure 4-14 : Débit global pour le scénario 2 sur le NoC 3x3 pour différentes charges71                                                                                    |

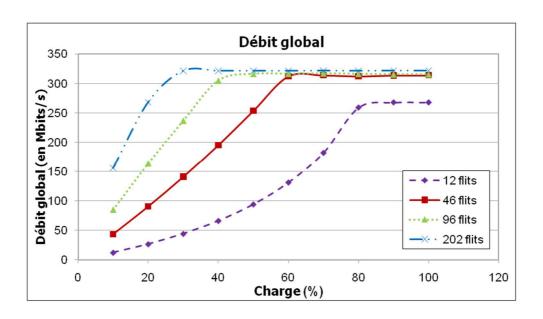

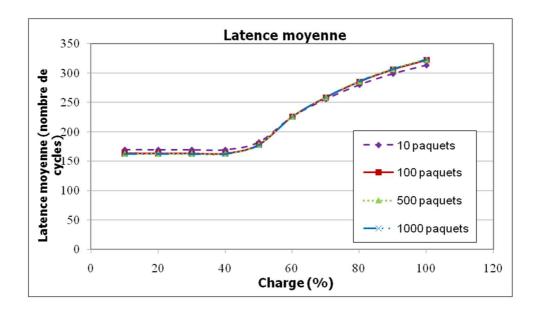

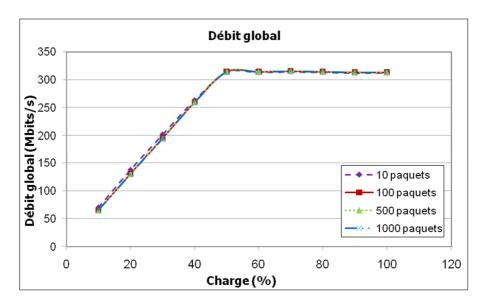

| Figure 4-15 : Latence moyenne pour le scénario 2 sur le NoC 3x3 en fonction de la taille de paquet                                                                         |

| Figure 4-16 : Débit global pour le scénario 2 sur le NoC 3x3 en fonction de la taille de paquet.                                                                           |

| Figure 4-17 : Latence moyenne pour le scénario 2 sur le NoC 3x3 en fonction du nombre de paquets                                                                           |

| Figure 4-18 : Débit global pour le scénario 2 sur le NoC 3x3 en fonction du nombre de paquets.                                                                             |

| Figure 4-19 : Les scénarii utilisés pour l'exploration des algorithmes de routage et de la position des blocs d'émulation pour le NoC Hermes                               |

| Figure 4-20 :Nombrede registres utilisés pour différents algorithmes de routage sur Hermes 74                                                                              |

| Figure 4-21 : Nombre de LUTs utilisées pour différents algorithmes de routage dans Hermes. 74                                                                              |

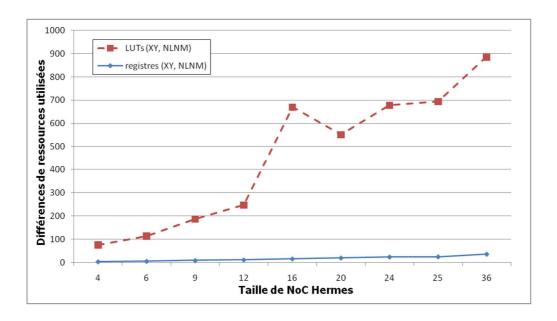

| Figure 4-22 : Différence du nombre de ressources entre les algorithmes de routage XY et NLNM                                                                               |

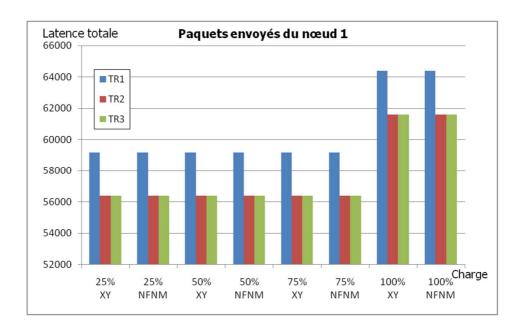

| Figure 4-23 : Latence totale pour chaque destinataire pour des paquets envoyés du nœud 1 avec une charge réseau variable avec l'algorithme de routage XY et NFNM           |

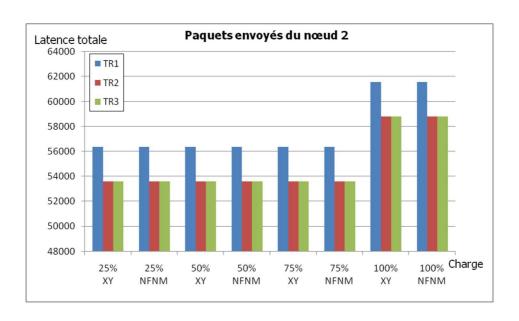

| Figure 4-24 : Latence totale pour chaque destinataire pour des paquets envoyés du nœud 2 avec une charge réseau variable avec l'algorithme XY et NFNM                      |

|                                                                                                                                                                            |

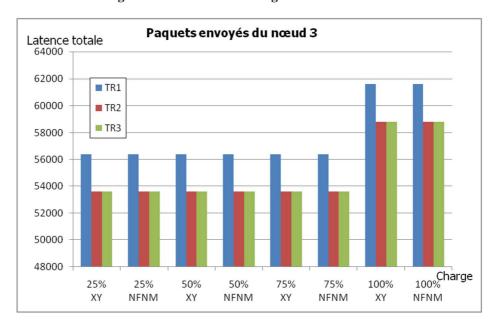

| Figure 4-25 : Latence totale pour chaque destinataire pour des paquets envoyés du nœud 3 avec une charge réseau variable avec l'algorithme XY et NFNM                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

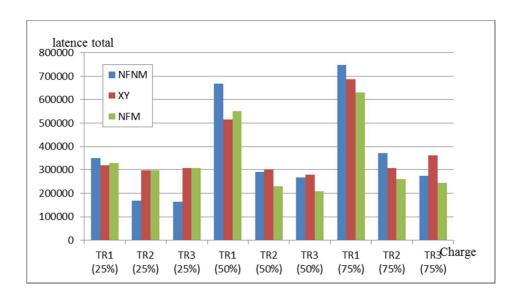

| Figure 4-26: Latence totale pour chaque destinataire pour des charges de 25%, 50% et 75% en fonction de 3 algorithmes de routage (1 déterministe et 2 semi adaptatifs)                                                                    |

| Figure 4-27 : Scénario utilisé sur un NoC 4x3 pour l'analyse du déploiement sur multi-FPGA.                                                                                                                                               |

| Figure 4-28: Plateforme d'émulation générée par le flot de conception proposée pour l'implémentation sur multi-FPGA (scénario 1: NLI= NR). L'adaptateur 1 est utilisé pour la communication inter-FPGA.                                   |

| Figure 4-29 : Plateforme d'émulation générée par le flot de conception proposée pour l'implémentation sur multi-FPGA (cas 2: NLI <nr). 2="" communication="" est="" inter-fpga<="" l'adaptateur="" la="" pour="" td="" utilisé=""></nr).> |

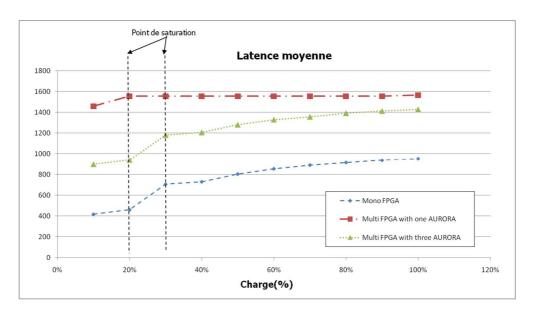

| Figure 4-30 : Latence moyenne pour les trois versions d'implémentations sur mono et multi-FPGA.                                                                                                                                           |

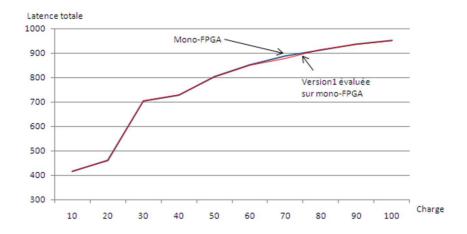

| Figure 4-31 : Latence estimée du NoC à partir de la latence multi-FPGA version 1et latence obtenue pour la version mono-FPGA                                                                                                              |

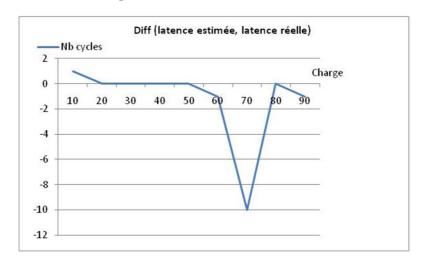

| Figure 4-32 : Différence entre la latence du NoC extraite de latence multi-FPGA version 1par rapport à l'implémentation du mono-FPGA                                                                                                      |

| Figure 4-33 : Architecture du NoC Hermes pour l'application d'imagerie spectrale                                                                                                                                                          |

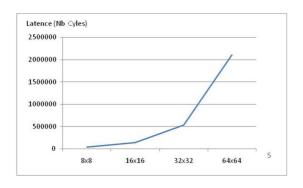

| Figure 4-34 : Latence de la communication acquisition=> moyenne pour différentes tailles de fenêtre (w=128, R=1)                                                                                                                          |

| Figure 4-35 : Latence de la communication acquisition=> moyenne pour différentes valeurs de longueurs d'onde (S=64, R=1)                                                                                                                  |

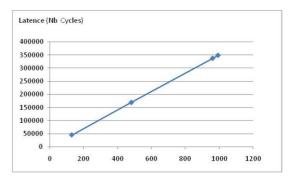

| Figure 4-36 : Latence de la communication moy_1=> XYZ_1 pour différentes valeurs de longueurs d'onde (S=64, R=1) pour une charge de réseau de 50%                                                                                         |

| Figure 5-1 : Flot de conception de STARSoC[79]                                                                                                                                                                                            |

| Figure 5-2 : L'infrastructure de SESAM                                                                                                                                                                                                    |

| Figure 5-3 : Flot de conception de la plateforme HeMPS                                                                                                                                                                                    |

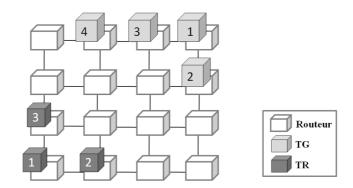

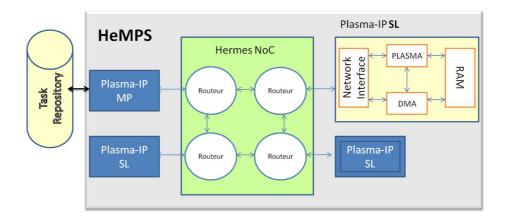

| Figure 5-4 : Architecture MPSoC-NoC HeMPS                                                                                                                                                                                                 |

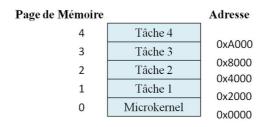

| Figure 5-5 : Configuration de la mémoire avec 5 pages                                                                                                                                                                                     |

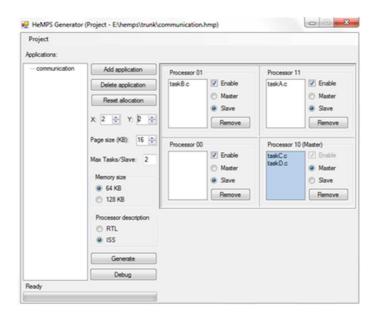

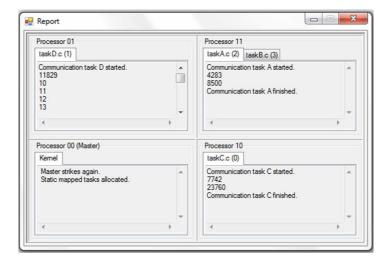

| Figure 5-6 : Interface graphique de l'outil HeMPS                                                                                                                                                                                         |

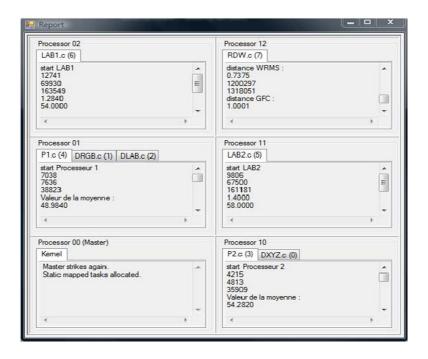

| Figure 5-7 : Interface de débogage HeMPS                                                                                                                                                                                                  |

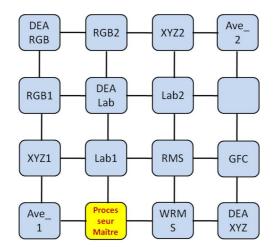

| Figure 5-8 : Placements des fonctions sur une architecture MPSoC 4x4                                                                                                                                                                      |

| Figure 5-9 : Placement des tâches de l'application sur l'outil HeMPS                                                                                                                                                                      |

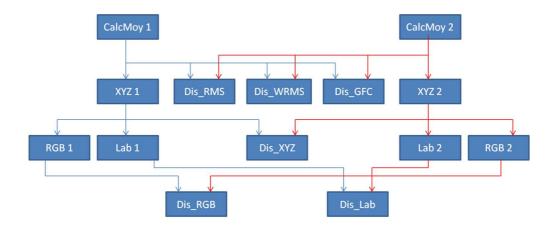

| Figure 5-10 : graphe flot de données de l'application                                               |

|-----------------------------------------------------------------------------------------------------|

| Figure 5-11 : Placements des tâches sur l'architecture 2x3 par l'utilisateur                        |

| Figure 5-12 : Rapport de débogage indiquant le placement final de l'ensemble des tâches 102         |

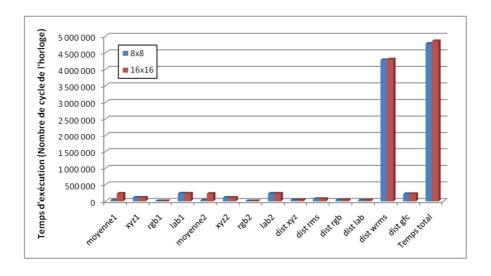

| Figure 5-13 : Les temps d'exécution pour chaque fonction en fonction du nombre de longueurs d'ondes |

| Figure 5-14 : Les temps d'exécution pour chaque fonction selon la taille de la région 103           |

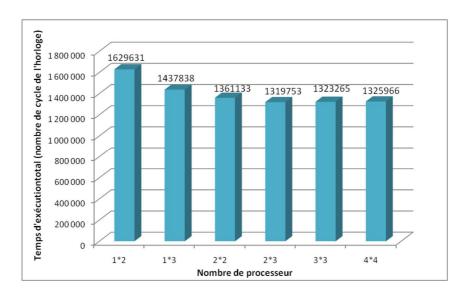

| Figure 5-15 : Temps d'exécution en fonction du nombre de processeurs                                |

| Figure 5-16 : La plateforme d'émulation de HeMPS sur FPGA                                           |

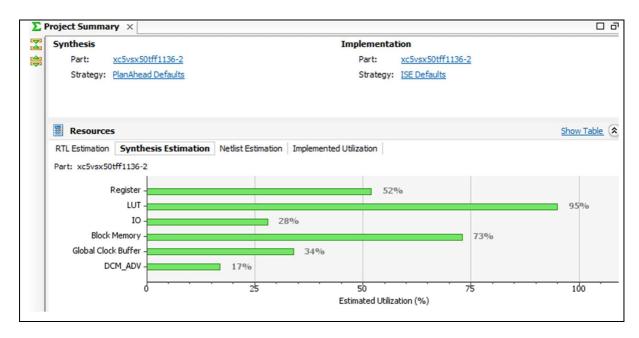

| Figure 5-17 : Rapport de synthèse pour FPGA xc5vsx50t                                               |

| Figure 5-18: Rapport du placement routage de la plateforme MPSoC NoC sur Virtex 5 108               |

| Figure 5-19 : Rapport de synthèse pour la plateforme MPSoC NoC sur FPGA xc6vlx240T 108              |

# Liste des Tableaux

| Tableau 2-1 : Temps d'exécution sur CPU (pour une région)                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Tableau 2-2 : NoC sur architecture mono-FPGA                                                                                             |

| Tableau 4-1 : Ressources utilisées des blocs TG et TR sur FPGA                                                                           |

| Tableau 4-2 : Nombre de registres utilisés par FPGA                                                                                      |

| Tableau 4-3 : Nombre de LUTs utilisées par FPGA                                                                                          |

| Tableau 4-4 : Nombre total de registres utilisés pour le déploiement d'un NoC sur plusieurs FPGAs                                        |

| Tableau 4-5 : Nombre total de LUT utilisées pour le déploiement d'un NoC sur plusieurs FPGAs                                             |

| Tableau 4-6 : Latences des différentes scénarii de l'algorithme d'authentification par émulation sur FPGA Virtex 5 pour R=1, W=128, S=64 |

| Tableau 5-1 : Temps d'exécution pour chaque fonction de l'application (16 longueurs d'ondes, 1 région, taille de fenêtre de 64 pixels)   |

| Tableau 5-2 : Temps d'exécution (nb cycles) pour la fonction WRMS en fonctions du nombre de longueurs d'ondes                            |

| Tableau 5-3 : Comparaison des valeurs des résultats de références sur CPU et les valeurs des résultats obtenus sur l'architecture HeMPS  |

# **Glossaire**

NoC Network-on-Chip

SoC System on Chip

FPGA Field Programmable Gate Array

IP Intellectual Property

CMOS Complementary Metal Oxide Semiconductor

MPSoC Multi-Processors System on Chip

GPU Graphical Processing Unit

GPP General Purpose Processor

SIMT Single Instruction Multiple Threads

NI Network Interface

NA Network adaptor

FLIT Flow control unIT

TR Récepteur de trafic

TG Générateur de trafic

SISD Single Instruction, Single Data

MIMD Multiple Instruction, Multiple Data

# Chapitre 1. Introduction

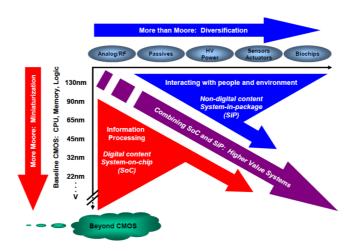

Le nombre de transistors sur puce croissant de manière exponentielle a permis d'augmenter de manière considérable la complexité des systèmes embarqués disponibles. Cette complexité est accrue par l'augmentation de la diversité des composants intégrés, diversité qui devient de plus en plus importante. Les progrès significatifs en termes de conception de circuit permettent dorénavant d'intégrer des composants analogiques ou d'autres types (par exemple mécanique) avec des transistors CMOS. Les performances des circuits ne se limitent plus à la miniaturisation mais à la diversification des composants. Cette diversification est prise en compte dans la loi « More than Moore », loi remplaçant la loi de Moore présentée par l'ITRS et présentée en Figure 1-1[1][2].Cette loi montre que les systèmes embarqués deviennent de plus en plus complexes et hétérogènes. Le nombre de blocs s'accroit ainsi que leurs diversités, ce qui devient une difficulté majeure dans la spécification et conception de ces systèmes. Cette difficulté va s'accroitre de manière significative avec l'augmentation du nombre et de la complexité des cœurs d'un système embarqué.

Figure 1-1 : Loi de Moore/ More than Moore : miniaturisation des fonctions numériques contre diversification fonctionnelle.

Les spécifications de la conception de systèmes sur puce (appelé SoC pour System On Chip) ainsi que leur validation sont à l'heure actuelle des challenges importants. L'espace de conception des architectures est très vaste, trop vaste pour qu'un concepteur système puisse définir des architectures adaptées parmi tous les composants de calcul, de mémorisation, de communication et de contrôle pour un ou des algorithmes de traitement du signal et de l'image. Le choix de l'architecture doit se faire dès les premières étapes du flot de conception afin de répondre aux contraintes de « Time To Market ». En effet, les premiers outils de codesign [3][4][5][6], apparus

dans les années 90, ont montré l'impossibilité d'un choix efficace des composants d'une architecture dans les dernières étapes du cycle de conception.

La simulation des systèmes multi composants hétérogènes devient également inadaptée car trop coûteuse en temps pour des simulations post-placement routage et trop loin du fonctionnement réel sur circuit pour les simulations fonctionnelles. La simulation est supplantée par le prototypage rapide et l'émulation qui permettent la vérification, l'exploration et la validation de système appropriées aux contraintes de « Time To Market » actuelles.

Les architectures embarquées conçues pour des applications de traitement de signal et d'images à contraintes temps réel fortes sont des architectures multiprocesseurs à plusieurs dizaines voire centaines de processeurs. On parle respectivement d'architectures « multicores » ou « manycores » (se référant respectivement à des dizaines et centaines de cœurs de calcul sur SoC). Ces cœurs bien souvent hétérogènes sont interconnectés via des architectures de communication de type réseau sur puce (NoC Network On Chip) afin de supporter un nombre élevé de cœurs pour des communications rapides et de faible consommation. L'architecture SoC qui utilise plusieurs processeurs connectés via le NoC est définie comme MPSoC(Multi-Processors System on Chip) [8]. Les circuits programmables notamment les FPGA (Field-Programmable Gate Array) sont utilisés pour l'émulation et le test des architectures, dans de nombreuses applications nécessitant le prototypage rapide d'application d'électronique numérique (télécommunication, traitement d'images, l'aéronautique...). Les circuits les plus évolués peuvent intégrer des cœurs de processeurs, logiciels ou matériels, des opérateurs câblés dédiés (appelés également blocs IP pour Intellectual Property) pour effectuer efficacement le prototypage de systèmes embarqués. A l'heure actuelle, un seul circuit FPGA ne possède pas assez de ressources pour supporter une architecture SoC complète. Ces architectures ont besoin d'être partitionnées sur plusieurs circuits reconfigurables, en général sur les plateformes multi-FPGA pour l'émulation et le test.

Dans le domaine de l'image, les applications en imagerie spectrale se substituent de plus en plus à l'imagerie couleur. L'imagerie spectrale permet de multiplier les intervalles spectraux d'intégration, améliorant la définition de la lumière d'une scène et un accès à des caractéristiques non visibles à l'œil nu. Ces algorithmes deviennent de plus en plus complexes, intégrant des données de type de plus en plus variés (avec des représentations et tailles variables) et augmentent le nombre de fonctions de calcul dans les dimensions spatiales et spectrales. Les contraintes temps réel de ces applications nécessitent des architectures dédiées telles des MPSoC à base de NoC présentées précédemment.

Il est donc nécessaire de pouvoir proposer des architectures embarquées hautes performances, dédiées aux algorithmes d'imagerie spectrale. Les architectures proposées doivent être paramétrables pour accueillir plusieurs applications d'imagerie spectrale sans repasser par le flot complet de la conception de l'architecture. Le choix des paramètres de l'architecture proposée doit se faire rapidement par le concepteur logiciel, sans pré-requis matériel et avec des solutions de vérification et d'émulation adaptées et disponibles immédiatement.

# 1.1 Contribution

La contribution de ce travail de thèse est de proposer un flot de conception, d'émulation et de validation d'architecture MPSoC basées sur un NoC générique. Cette architecture est dédiée aux applications d'imagerie spectrale, notamment pour des applications d'authentification d'œuvres d'art. Le flot de conception proposé permet de générer une plateforme mono ou multi-FPGA et facilite l'exploration de l'espace de conception et l'analyse des performances.

Il est apparu au cours de ces travaux qu'une des contraintes majeures provenait des échanges de données entre les éléments de calcul. Aussi un travail plus approfondi sur l'évaluation des performances et l'amélioration des caractéristiques d'un NoC générique est réalisé. Une contribution plus spécifique consiste à définir les blocs d'émulation adaptés à l'évaluation et à l'exploration d'architecture. Une bibliothèque de générateurs et de récepteurs de trafic développés en VHDL permet à l'utilisateur de sélectionner les blocs d'émulation adaptés à ses besoins. Les générateurs permettent de simuler tous types de trafic, d'un émetteur ou de plusieurs émetteurs vers un ou plusieurs récepteurs ciblés en utilisant des tailles de paquets variables. De la même manière, les récepteurs permettent de récupérer des informations de performances (telle la latence d'un flit, d'un paquet) ou d'extraire les données du paquet. Les mesures de performances tiennent compte des éléments additionnels nécessaires aux communications entre FPGA pour une plateforme multi-FPGA.

# 1.2 Plan du manuscrit

Ce manuscrit, organisé en quatre chapitres, présente l'étude et l'exploration d'une architecture générique sur FPGA pour des algorithmes d'imagerie multispectrale. Cette architecture est destinée à des équipements embarqués et portables, nécessitant de supporter des applications variées d'imagerie spectrale.

### 1.2.1 Applications et principes de base des architectures

Le premier chapitre de ce manuscrit présente les algorithmes d'imagerie multispectrale ainsi qu'une description succincte des architectures de communication pour les systèmes embarqués appelés réseaux de communication sur puce. Ce chapitre présente dans un premiers temps le principe de l'imagerie spectrale puis décrit une application dédiée à l'authentification d'œuvres d'art en imagerie multispectrale. Nous présentons ensuite deux solutions d'architectures parallèles standard permettant d'accélérer éventuellement les performances de calcul de cet algorithme : les architectures PC multicoeurs et les architectures GPU (Graphical Processing Unit). Nous analysons les performances c'est à dire les forces et faiblesses de chacune de ces architectures. Ensuite, nous effectuons une étude du réseau de communication sur les systèmes sur puce (SoC) et systèmes multiprocesseurs sur puce (MPSoC), ces architectures constituant les plateformes de développement du travail de thèse.

### 1.2.2 Proposition d'une méthodologie pour la conception et l'exploration de NoC

Après une étude des architectures d'émulation des réseaux de communication sur puce NoC, ce deuxième chapitre aborde la proposition de notre méthodologie pour la conception d'une plateforme d'émulation de NoC dédiée à la validation et l'exploration de l'espace de conception des NoCs. Cette nouvelle méthodologie, basée sur diverses bibliothèques développées et insérées dans le flot de conception, permet la génération des architectures adaptables à des plateformes mono-FPGA ou multi-FPGA afin d'évaluer efficacement les performances du NoC et d'explorer les architectures de NoC les plus adaptées aux besoins de l'application ciblée.

# 1.2.3 Implémentation et évaluation des NoC pour l'évaluation et l'exploration de l'espace de conception

Le troisième chapitre de ce manuscrit cible l'implémentation d'une plateforme générée par la méthodologie proposée dans le chapitre précédent. Cette plateforme d'émulation permet l'évaluation des performances mais également l'exploration de l'espace de conception de l'architecture, ceci grâce au développement de composants génériques paramétrables disponibles dans les bibliothèques associées au flot. Tout d'abord, nous proposons un ensemble de blocs d'émulation contenant les générateurs de trafic et les récepteurs de trafic. Nous présentons l'architecture du NoC Hermes utilisée dans la conception de la plateforme d'émulation. Cette dernière est implémentée sur FPGA Xilinx afin d'étudier des performances et définir les limitations d'une telle architecture. Ainsi un flot similaire ciblant des architectures multi-FPGA est proposé offrant ainsi une extensibilité de la plateforme d'émulation à des plateformes multi-composants. L'analyse des performances est étudiée en fin de chapitre.

# 1.2.4 Expérimentation : Implantation d'algorithmes d'imagerie multi-spectrale

Le dernier chapitre de ce manuscrit présente une solution d'une architecture MPSoC obtenue à l'aide de notre flot de conception. L'architecture est composée d'un ensemble de processeurs Plasma autour du NoC Hermes. Nous avons utilisé l'outil HeMPS, développé par l'université PUCRS qui permet de générer une plateforme de simulation ou d'émulation sur FPGA. Ceci nous permet de comparer différentes architectures et de valider nos travaux sur l'implantation MPSoC basée sur un NoC pour l'algorithme d'imagerie multi-spectrale.

Le manuscrit se termine par une conclusion générale ainsi que des perspectives.

# Chapitre 2. Applications et principe de base des architectures

# 2.1 Imagerie couleur et multispectrale

### 2.1.1 Imagerie couleur

L'imagerie couleur est une image numérique qui contient des informations de couleur pour chaque pixel [8].Un espace de couleurs associe des nombres aux couleurs visibles. Compte tenu des limites de la vision humaine, ces nombres se présentent généralement sous la forme de triplets. Chaque couleur de lumière peut donc être caractérisée par un point dans un espace à trois dimensions. Il existe plusieurs espaces couleur (RGB, XYZ, L\*a\*b ...), les espaces les plus utilisés étant présentés ci-dessous.

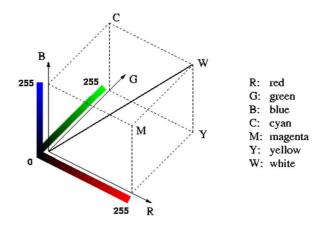

# 2.1.1.1 L'espace de couleur RGB

C'est l'espace de base, supporté nativement par la plupart des cartes vidéo. En combinant les trois primitives RGB (respectivement Red, Green et Blue pour rouge vert et bleu), il est possible d'obtenir, ou presque, toutes les couleurs du visible.

Le mélange des pigments de peinture permet d'obtenir toutes les couleurs possibles par filtrage de la lumière en retirant des composantes, et en ne réfléchissant que les couleurs désirées [10]. Ceci est appelé un système soustractif. Le système de couleur RGB est un système additif car la lumière est ajoutée. Ainsi dosées, les trois composantes permettent de représenter un grand nombre de couleurs, mais certaines couleurs visibles par l'œil n'ont pas de représentation dans cet espace.

Chaque axe du cube, de la Figure 2-1 représente des valeurs de rouge, de vert, ou bleu dans l'intervalle [0.255]. L'axe rouge, étiqueté R, montre l'échelle de couleurs associée. Les axes vert et bleu sont illustrés de la même manière. La valeur 0 signifie que le moniteur n'émet pas la couleur primaire et la valeur 255 signifie qu'il émet le maximum. Les valeurs entre 0 et 255 représentent les gradations dans l'intensité de la couleur.

Figure 2-1: Le cube de couleurs RGB [11]

Comme l'indique l'espace de couleur, les couleurs agissent comme des vecteurs. Ces couleurs peuvent être combinées par addition et soustraction pour obtenir d'autres couleurs dans le cube. Ainsi, l'origine du cube, ou  $0^R$   $0^G$   $0^B$ , représente l'absence totale de couleur, c'est à dire le Noir. L'extrémité la plus éloignée de l'origine est la somme des intensités les plus élevées de rouge, de vert, et de bleu, ou  $255^R$   $255^G$   $255^B$ . Ceci correspond à la couleur du Blanc (étiquetée par W sur la Figure 2-1). Les autres coins du cube représentent les diverses couleurs primaires et secondaires. Nous avons déjà rencontré le rouge, le vert, et le bleu. Les trois couleurs restantes sont cyan, magenta, et jaune.

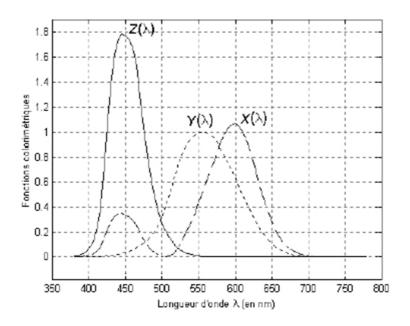

#### 2.1.1.2 L'espace de couleur XYZ

L'espace couleur CIE (Commission Internationales de l'Eclairage) XYZ a été défini afin de corriger certains défauts présents dans l'espace RGB. Cet espace résulte les travaux de Judd [12] et est constitué de trois primaires X, Y et Z, dites virtuelles. Ainsi, l'espace couleur XYZ présente les propriétés suivantes :

- Les triplets décrivant chaque couleur en fonction de ses primaires ont tous des valeurs positives pour les spectres visibles (Figure 2-2);

- La fonction Y(λ) représente approximativement la sensibilité de l'œil humain à la luminosité. Par conséquent, la composante Y est habituellement considérée comme la composante luminance du spectre incident;

- Chaque spectre d'égale énergie est associé à un triplet dont toutes les composantes sont égales [12].

Figure 2-2 : Les fonctions colorimétriques  $X(\lambda)$ ,  $Y(\lambda)$  et  $Z(\lambda)$

Le passage de l'espace RGB à l'espace XYZ s'effectue simplement grâce à une transformation linéaire pouvant être interprétée comme un changement de base. L'équation de transformation d'espace est la suivante [13] :

$$\begin{bmatrix} +0.431 & +0.342 & +0.178 \\ -0.222 & +0.707 & +0.071 \\ +0.020 & -0.130 & -0.939 \end{bmatrix} \begin{bmatrix} R \\ G \\ R \end{bmatrix} = \begin{bmatrix} X \\ Y \\ Z \end{bmatrix}$$

Équation 2-1

L'équation de passage de l'espace XYZ à RGB est la suivante:

$$\begin{bmatrix} +3.059 & -1.393 & -0.475 \\ -0.968 & +1.875 & +0.042 \\ +0.069 & -0.230 & +1.069 \end{bmatrix} \begin{bmatrix} X \\ Y \\ Z \end{bmatrix} = \begin{bmatrix} R \\ G \\ B \end{bmatrix}$$

Équation 2-2

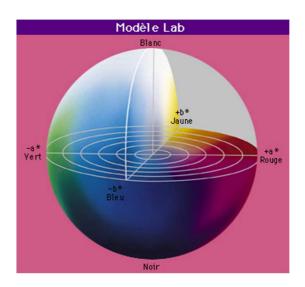

## 2.1.1.3 L'espace CIE L\*a\*b\*

L'espace CIE L\*a\*b\* est un modèle de représentation des couleurs développé en 1976 par la CIE. Comme tous les systèmes issus du système CIE XYZ, il caractérise une couleur à l'aide d'un paramètre d'intensité correspondant à la luminance et de deux paramètres de chrominance qui décrivent la couleur. Il a été spécialement étudié pour que les distances calculées entre couleurs correspondent aux différences perçues par l'œil humain.

- La combinaison L\* est la clarté, allant de 0 (noir) à 100 (blanc).

- La composante **a\*** représente la gamme de l'axe rouge (valeur positive) ->vert (négative) en passant par le blanc (0) si la clarté vaut 100.

• La composante **b\*** représente la gamme de l'axe jaune (valeur positive) -> bleu (négative) en passant par le blanc (0) si la clarté vaut 100.

Figure 2-3 : Modèle de représentation dans l'espace couleur L\*a\*b\* [14]

Une difficulté majeure de ce système est l'utilisation d'un système mixte de repérage des points de couleur. La saturation est mesurée de manière cartésienne, alors que la teinte et la luminosité sont mesurées de manière angulaire (Figure 2-3).

Figure 2-4 : Représentations cartésiennes et polaires [14]

La conversion de l'espace RGB vers l'espace L\*a\*b\* nécessite une conversion intermédiaire dans l'espace de couleur XYZ. Les équations permettant de passer par l'espace intermédiaire sont les suivantes [14]:

$$x = x_{max} \left( p + \frac{a^*}{500} \right)^3$$

$y = y_{max} * p^3$   $z = z_{max} \left( p - \frac{b^*}{200} \right)^3$  Où  $p = \frac{l^* + 16}{116}$  Équation 2-3

et l'inverse est donné par :

$$L = 116 \left( \left( \frac{y}{y_{max}} \right)^{\frac{1}{3}} \right) - 16 \qquad a^* = 500 \left( \left( \frac{x}{x_{max}} \right)^{\frac{1}{3}} - \left( \frac{y}{y_{max}} \right)^{\frac{1}{3}} \right) b^* = 200 \left( \left( \frac{y}{y_{max}} \right)^{\frac{1}{3}} - \left( \frac{z}{z_{max}} \right)^{\frac{1}{3}} \right)$$

#### **Équation 2-4**

### 2.1.2 Imagerie Multispectrale

L'imagerie multispectrale est une technique développée à l'origine pour le traitement de l'image dans le spectre. En imagerie couleur classique, on acquiert 3 images. En imagerie multispectrale on acquiert beaucoup plus d'images, chaque image correspondant à une bande très étroite du spectre. On a ainsi une définition beaucoup plus précise de la lumière réfléchie par une surface et on peut ainsi accéder à des caractéristiques non visibles à l'œil nu. Les domaines d'utilisation de l'imagerie sont de plus en plus variés. De ce fait les applications traditionnellement en couleur s'orientent vers l'imagerie spectrale (multispectrale ou hyperspectrale).

Figure 2-5: Imagerie multispectrale.

La Figure2-5représente une image multispectrale. Les images spectrales obtenues à différentes longueurs d'ondes sont extraites d'une scène, le nombre de longueurs d'onde pouvant couvrir le domaine du visible mais également au-delà. Ainsi le nombre d'images spectrales constituant l'image multispectrale peut être élevée. Les bandes spectrales peuvent être choisies en fonction de longueurs d'ondes caractéristiques des matières ou des produits à analyser.

# 2.2 Processus d'authentification en Imagerie Multispectrale

Une des applications possible des algorithmes d'imagerie multispectrale est l'authentification d'objets. Le domaine applicatif choisi concerne l'authentification d'œuvres d'art, notamment des

peintures. L'objectif est de déterminer si l'œuvre d'art présente est l'originale ou une copie. Pour le processus d'authentification d'œuvres d'art, nous comparons une œuvre mise à notre disposition avec un ensemble d'informations caractérisant l'œuvre de référence (œuvre originale). Les informations relatives à l'image originale correspondent à des régions significatives. Ainsi les données d'entrée sont :

- OR (Original Region): sont les régions significatives de l'œuvre de référence dans les différentes longueurs d'ondes. Ces données sont enregistrées dans une base de données.

- CR (Compared Region) : sont les régions significatives de l'œuvre à authentifier dans les différentes longueurs d'ondes. Ces régions proviennent d'une caméra spectrale adaptée pour l'acquisition des régions de l'œuvre à différentes longueurs d'onde.

# 2.2.1 Principe de l'algorithme d'authentification pour les œuvres d'arts

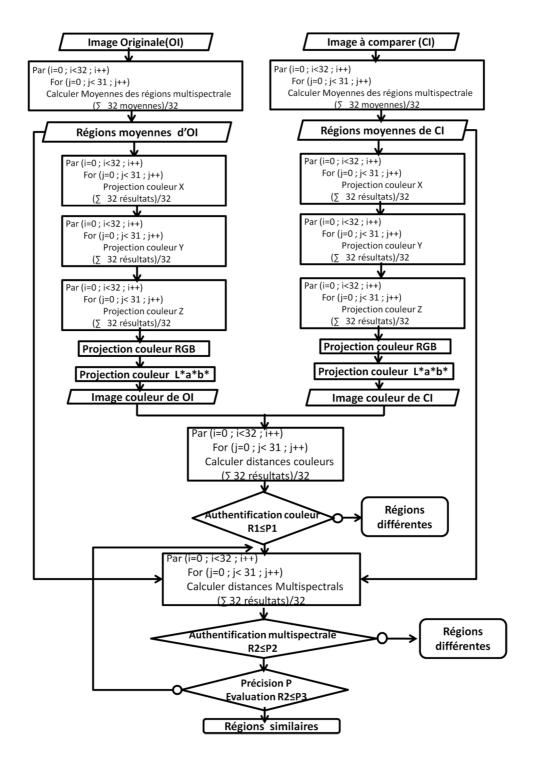

L'algorithme d'authentification s'effectue dans des espaces couleurs puis en multispectral si nécessaire, plus précisément si le résultat de l'authentification indique que l'œuvre à authentifier est l'originale (dans le cas d'une fausse authentification, les analyses dans le domaine multispectrale ne sont pas conduites). L'algorigramme de l'application proposé est donné en Figure 2-6.

L'algorithme d'authentification se base sur deux étapes principales : une comparaison entre la OR et la CR dans certains espaces de couleur (espace spectral de base, l'espace RGB, l'espace XYZ, l'espace L\*a\*b, etc.) puis une comparaison entre la OR et la CR dans l'espace spectral. Le processus d'authentification se décompose en cinq étapes:

- 1) Moyenne spatiale des régions : les régions provenant de la base de données et de la caméra sont moyennées pour chaque région et pour chaque longueur d'onde.

- 2) Projection couleur : selon l'espace de couleurs de référence choisi, les données originales de spectres de la OR / CR sont transformées en données couleurs.

- 3) Authentification couleur : le résultat R1 correspondant à la distance couleur entre La région originale et celle à comparer. Ce résultat est obtenu en choisissant au préalable un calcul de distance approprié. Une comparaison entre le résultat R1 et la précision P1 (définie au préalable en fonction de l'expérimentation) est effectuée. Si le résultat de la comparaison correspond, le processus d'authentification est affiné par un passage dans l'espace multispectral (étape 3). Si R1 est différent de P1 (la comparaison ne correspond pas), l'OR et le CR sont différents, le processus s'arrête car l'objet à authentifier est faux.

- 4) Authentification multispectrale : le résultat R2 correspondant à la distance dans l'espace spectral est calculé en choisissant un calcul de distance spectral. Une comparaison entre le résultat R2 et la précision P2 (définie au préalable) est effectuée. Si le résultat de la comparaison correspond, le processus d'authentification multispectrale peut être affiné en augmentant le nombre de longueurs d'ondes utilisé. Si une plus grande précision n'est pas nécessaire, le résultat de l'authentification est fait dans l'étape 4 afin de définir si l'objet est authentifié ou non.

- 5) Résultat de l'authentification : si le résultat indique une différence significative entre une précision (P2, P3 ...) et R2, cela signifie que l'œuvre d'art n'est pas l'originale. Sinon, l'œuvre d'art est bien l'originale.

Figure 2-6 : Processus d'authentification d'œuvres d'art en imagerie spectrale.

Les transformations dans les différents espaces couleurs ayant été présentées dans le paragraphe précédent, la présentation de l'algorithme porte sur les calculs de distance couleur et spectral. Les calculs de distances choisis sont ceux les plus couramment utilisés dans les applications d'authentification et répertoriés en littérature.

## 2.2.2 Calculs de distance dans des espaces couleurs

# 2.2.2.1 Goodness of Fit Coefficient: GFC

Le calcul GFC est basé sur l'inégalité de Schwartz et est décrit par l'équation suivante [15] :

$$GFC = \frac{|\Sigma_{j} R_{m}(\lambda_{j}) R_{e}(\lambda_{j})|}{\sqrt{\Sigma_{j} [R_{m}(\lambda_{j})]^{2}} \sqrt{\Sigma_{j} [R_{e}(\lambda_{j})]^{2}}}$$

Équation 2-5

Où  $R_{\rm m}(\lambda_{\rm j})$ est la donnée spectrale d'origine à la longueur d'onde  $\lambda_{\rm j}$ ,  $R_{\rm e}(\lambda_{\rm j})$ est la donnée spectrale d'estimation à la longueur d'onde  $\lambda_{\rm j}$ .

Le résultat GFC doit être compris entre 0,999 et 0,9999 pour considérer que l'on obtient respectivement une bonne et une excellente correspondance spectrale.

### 2.2.2.2 Viggiano Index Mv

Cette méthode est basée sur la somme des valeurs  $\Delta E^*$  d'une longueur d'onde entre les deux spectres, dans lequel ils diffèrent seulement d'une longueur d'onde particulière. En pratique, une approximation linéaire de ces  $\Delta E^*$  est utilisée. Le résultat est une somme pondérée des valeurs absolues des différences entre les deux spectres [16]. L'indice de comparaison spectrale [16]est calculé comme suit :

$$M_v = \sum_{\lambda=1}^n w(\lambda) \|\Delta \beta(\lambda)\|$$

Équation 2-6

Où  $\Delta \beta(\lambda)$  est la différence entre les deux spectres.  $w(\lambda)$  est défini suivant l'équation :

$$w(\lambda) = \sqrt{\left(\frac{dL^*}{d\beta(\lambda)}\right)^2 + \left(\frac{da^*}{d\beta(\lambda)}\right)^2 + \left(\frac{db^*}{d\beta(\lambda)}\right)^2}$$

Équation 2-7

# 2.2.3 Calculs de distance dans l'espace spectral

Les calculs de distances choisis pour des images multispectrales sont RMS et WRMS.

#### 2.2.3.1 Root Mean Square Error: RMS

La fonction RMS, Root Mean Square Error est calculée au moyen de l'équation suivante :

$$RMS = \sqrt{\frac{1}{N} \sum_{j} \left\| S_{1\lambda j} - S_{2\lambda j} \right\|^{2}}$$

Équation 2-8

Où S correspond au spectre à calculer,  $\lambda$  la longueur d'onde et N le nombre de longueur d'ondes.

Cette méthode de calcul de distance spectral est la plus utilisée, car facile à calculer. Cependant elle ne considère pas la vision humaine [17].

## 2.2.3.2 WRMS (Inverse Reflectance)

Le calcul WRMS considère un ensemble de poids associé à chaque longueur d'onde contrairement au calcul RMS. La distance spectrale est obtenue au moyen de l'équation :

$$wrms = \sqrt{\frac{\sum_{\lambda=1}^{n} (\sqrt{w(\lambda) \Delta \beta(\lambda)})^{2}}{n}}$$

Équation 2-9

Où  $w(\lambda)$  est le poids, n est le nombre de longueurs d'ondes,  $\Delta\beta(\lambda)$  est la différence entre les deux spectres [19].

Cette méthode utilise différents poids pour les couleurs foncées et les couleurs claires.

#### 2.2.4 Conclusion

La description de l'algorithme et des fonctions utilisées montre la nécessité de concevoir une architecture matérielle dédiée qui réponde à plusieurs contraintes :

- Il est nécessaire d'avoir des puissances de calcul importantes pour répondre à des contraintes temps réel fortes,

- Les structures de ces blocs doivent s'adapter aux paramètres variables de l'application, à l'ajout de nouvelles fonctions, à la modification de la représentation du flot de donnée de l'application,

- Les capacités de communication doivent être performantes et adaptables,

- L'architecture doit pouvoir considérer des formats de données variables et multiples pour les communications et les opérations de calcul, pour répondre à la méthodologie AAA (Adéquation Algorithme Architecture).

# 2.3 Les architectures programmables embarquées pour l'algorithme d'authentification

Il est possible d'implanter l'algorithme précédemment présenté sur plusieurs architectures programmables comme un processeur classique (CPU) ou des processeurs graphiques(GPU). L'objectif est de montrer les limitations et les avantages de ces architectures par rapport aux architectures MPSoC sur FPGA.

Dans la famille des solutions programmables dans le domaine de l'embarqué, nous distinguons les processeurs généralistes et les processeurs spécialisés embarqués.

### 2.3.1 Processeur généraliste dans l'embarqué : AMD Athlon 64

Un processeur généraliste, appelé « General Purpose Processor » (GPP), permet la plus grande versatilité en termes de calcul. Dans le domaine de l'embarqué, ce type de processeur est généralement utilisé pour du contrôle global ou des applications de haut niveau.

L'AMD Athlon 64 est le processeur généraliste utilisé pour évaluer l'algorithme d'authentification. C'est un microprocesseur 64 bits basé sur l'architecture K8 et conçu pour les ordinateurs de bureau. Ces microprocesseurs comprennent toutes les fonctions de base de micro-architecture K8. Nous pouvons citer le découpage 128 Ko de cache niveau 1, le cache niveau 2 exclusif 512 Ko ou 1 Mo, la technologie AMD64, Enhanced Virus Protection, et le jeu d'instructions spécifiques Intel SSE2 (Streaming SIMD Extensions). Le jeu d'instructions SSE3 a été ajouté sur tous les processeurs Athlon 64 bits.

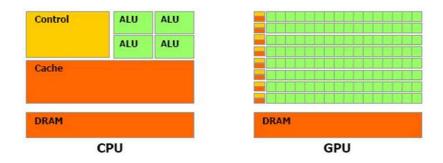

La stratégie des architectures CPU, présentée en Figure 2-9, est d'exécuter une tâche la plus rapidement possible. Ces stratégies utilisent la mémoire cache, le prefetching des instructions et l'exécution spéculative. Les architectures sont de type SISD ou MIMD pour des CPU double ou quadri-cœurs.

#### 2.3.2 Processeur spécialisé : GPU

Les processeurs spécialisés sont conçus et adaptés pour certains types de calculs. Lorsque le type d'application est ciblé, il s'agit de concevoir des unités fonctionnelles spécifiques adaptées aux besoins de l'algorithme dans le processeur. La conception d'une telle architecture dédiée permet d'accélérer les temps de calcul.

Un GPU (Graphics Processing Unit) est un microprocesseur présent sur les cartes graphiques au sein d'un ordinateur ou d'une console de jeux vidéo, et est dédié à l'accélération graphique 3D. Dans les années passées, les puissances de calcul des GPU programmables ont progressé de manière significative, comme représenté dans la Figure 2-7.

|                    | Peak<br>GFLOPS | Year |                        | Peak<br>GFLOPS | Year |

|--------------------|----------------|------|------------------------|----------------|------|

| Intel Pentium 4    | 7              | 2003 | Nvidia Geforce 6800    | 54             | 2004 |

| Intel Pentium D    | 13             | 2005 | Nvidia Geforce 7800    | 165            | 2005 |

| Intel Core 2 Duo   | 23             | 2006 | Nvidia Geforce 8800    | 576            | 2006 |

| Intel Core 2 Quad  | 51             | 2007 | Nvidia Geforce GTX 280 | 933            | 2008 |

| Intel Core i7 Quad | 70             | 2008 | Nvidia Geforce GTX 480 | 1,350          | 2010 |

| Intel Core i7 Hex  | 109            | 2010 | Nvidia Geforce GTX 580 | 1,580          | 2011 |

| Intel Ivy Bridge   | 130            | 2012 | Nvidia Kepler          | 3,200          | 2012 |

| Intel Haswell      | 400            | 2014 | Nvidia Maxwell         | 5,000          | 2014 |

Figure 2-7: Evolution de processeurs généralistes / GPU[20]

Le GPU est particulièrement bien adapté au problème d'adressage qui peut être exprimé pour des calculs de données parallèles. Un même programme est exécuté pour chaque donnée, le besoin en flot de contrôle est faible. Dans un GPU, la latence d'un accès à la mémoire peut être cachée par le calcul au lieu d'utiliser les grandes mémoires caches de données.

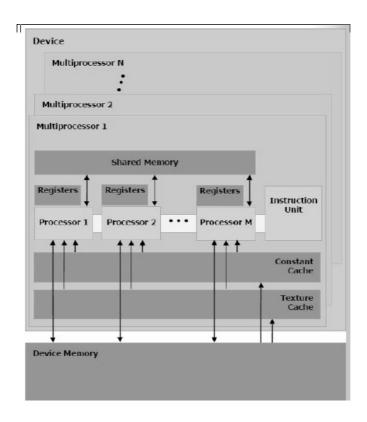

Figure 2-8: Architecture GPU NVIDIA Geforce [22]

Les GPUs les plus courants présentent des solutions efficaces pour l'implantation d'algorithmes graphiques, des applications 3D telles que la reconstruction en tomographie en raison de leur haut niveau de parallélisme. De plus, les GPUs NVIDIA sont efficacement et facilement programmables dans l'environnement CUDA. La famille de NVIDIA Geforce GT200 (Figure 2-8) a au maximum 30 multiprocesseurs (MP) fonctionnant en streaming. Chaque multiprocesseur dispose de 8 processeurs pour notre architecture. Les MP fonctionnent de manière asynchrone et sans possibilité de communication entre eux. Chaque MP travaille en mode SIMD, ce qui signifie que chaque processeur d'un même MP exécute la même instruction en utilisant le même type de donnée. Un code non-incrémental est parallélisé afin d'exécuter efficacement sur les 1 × 8 multi-threaded stream processeurs. Les threads sont regroupés en blocs (32x1 threads dans notre cas) qui sont définis au moment de l'exécution d'un bloc pour chaque multiprocesseur. Chaque couple de multiprocesseurs est associé à une mémoire cache de texture2D et une mémoire de données. Les processeurs disposent de quelques registres. De plus, le GPU offre une grande bande passante mémoire (BWmem = 112 Go / s dans notre cas) et utilise la virgule flottante pour les calculs. Toutceci permet de paralléliser efficacement les boucles.

Le GPU est programmable en utilisant le langage C standard avec quelques extensions sans aucune connaissance du pipeline graphique.

La stratégie des architectures GPU est l'exécution d'un nombre important de tâches en parallèle (Figure 2-9). Le parallélisme de donnée peut couvrir jusqu'à 1000 tâches et le pipeline est exploité. Les GPU supportent le multitâche massif et cachent les latences avec du calcul et non pas des mémoires caches. L'architecture GPU est de type SIMT (Single Instruction Multiple Threads) avec une structure de parallélisme hiérarchique.

Figure 2-9 : Stratégie des architectures CPU et GPU.

# 2.4 Performances sur CPU et GPU

Les spécifications suivantes sont choisies pour l'algorithme présenté dans le chapitre précédent dans le cas de l'authentification d'une peinture :

- Nombre de régions = 2 000.

- Nombre de longueurs d'onde pour chaque région = 128, 480, 960, 992.

- Tailles de la fenêtre (pour la moyenne) = 1x1, 2x2, 4x4, 8x8, 16x16, 32x32, 64x64 pixels.

L'algorithme paramétrable est d'abord exécuté sur une nouvelle génération de PC dual-core, ensuite sur une génération de GPU GTX280 afin d'obtenir différentes performances.

### 2.4.1 Exécutions sur CPU

L'algorithme d'authentification est exécuté sans optimisations, à partir de fonctions C décrivant chaque nœud de l'application. Les spécifications du CPU sont les suivantes :

- AMD Athlon64x2 Dual Core Processeur 4800+ 2,5GHz,

- 2Go de RAM

- L'accès aux régions et aux spectres se font de manière identique pour les systèmes embarqués visés. Ainsi le chargement de chaque région ou de chaque spectre est fait de manière successive à partir d'une mémoire globale.

Tableau 2-1: Temps d'exécution sur CPU (pour une région)

|                         | Total | Moyenne | Accès de | Distance       |  |

|-------------------------|-------|---------|----------|----------------|--|

|                         |       | (64x64) | fichier  | multispectrale |  |

| Temps d'exécution (sec) | 5.654 | 0.234   | 5.42     | 0.05           |  |

- Le temps d'exécution sur un CPU est environ de 188 minutes (soit 2h30) pour 2000 régions avec des accès de fichiers sur disque dur standard (lectures de coefficients, des régions pour CR et OR).

- Les accès au fichier correspondent à la majeure partie du temps d'exécution avec un temps de lecture et d'écriture de 5.42 s. Ce temps est relativement long car il est lié aux performances de la mémoire utilisée dans le PC d'expérimentation. L'accès aux fichiers pour les 2000 régions pourrait se faire beaucoup plus vite avec l'utilisation de mémoires externes rapides. Par exemple, on peut espérer atteindre environ 10 minutes au lieu de 2h30 pour un disque dur de 250 Mo/s d'accès en pipeline.

- Le calcul de la moyenne constitue la fonction la plus gourmande en temps de calcul. Des

optimisations de ce temps de calcul sont difficilement envisageables, les régions étant

distinctes les unes des autres.

#### 2.4.2 Exécutions sur GPU (Graphics Processing Unit)

La plateforme de GPU utilisée dans notre cas est GTX280 Nvidia Geforce. Les spécifications sont les suivantes :

- 240 stream processeurs

- Core clock 576MHz

- 1GB de mémoireDDR3

Les techniques d'accélération utilisées pour l'algorithme sont basées sur le parallélisme de données. Cette technique décompose les longueurs d'onde sur chaque processeur pour réaliser du multitâche. Le nombre de longueurs d'onde est choisi en fonction du nombre de processeurs de chaque MP. Les processeurs du MP exécutent une fonction et renvoient le résultat vers un processeur pour le calcul final de la fonction à exécuter. L'implantation de l'algorithme se résume donc à l'exécution d'une fonction en parallèle puis de la même fonction en séquentiel pour les calculs de moyenne, les projections dans l'espace X, l'espace Y et Z ainsi que les calculs de distance couleur et de distance multispectrale.

Figure 2-10 : Algorithme d'authentification parallélisé sur une architecture GPU à 16 processeurs par MP.

L'algorithme proposé pour une implantation sur GPU est donné en Figure 2-10. L'exécution en parallèle se décrit par la fonction par{}. L'architecture contient 16 processeurs par MP, chaque processeur pouvant effectuer deux tâches. Il est donc possible d'exécuter 32 calculs en parallèle. Ainsi pour le calcul des moyennes des 992 longueurs d'onde, on effectue 32 moyennes en parallèles

31 fois. Ces résultats sont envoyés ensuite sur un seul et même processeur afin de calculer le résultat final. Ceci correspond aux boucles imbriquées des fonctions de moyenne et de la fonction qui la suit de la Figure 2-10.

La localité 2D de l'architecture GPU est préservée en utilisant la mémoire cache de texture 2D. Les résultats des fonctions exécutées en parallèle étant réutilisés par la fonction séquentielle associée, il est nécessaire de considérer l'organisation mémoire des résultats et la synchronisation des tâches.

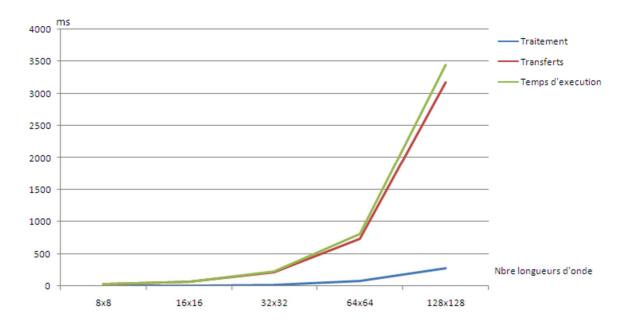

Les performances du GPU pour une seule région sont présentées dans la Figure 2-11. Sur cette figure les courbes décrivent les temps de calcul de la moyenne pour différentes tailles de région, le temps des accès à la mémoire (défini comme le temps de transfert) ainsi que le temps total d'exécution de l'algorithme.

Figure 2-11 : Temps de traitement, d'accès mémoire et temps d'exécution total

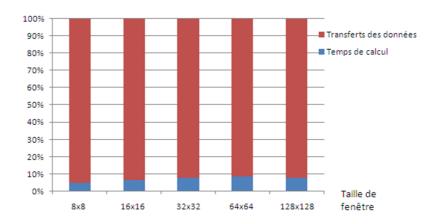

Comme nous pouvons le voir, le temps de transfert des données est important par rapport au temps de traitement lui-même. De ce fait, le taux d'occupation est faible. Le calcul représente entre 5% et 10% du temps total pour l'ensemble des paramétrages testés pour l'application spectrale. La Figure 2-12 représente le pourcentage d'occupation du GPU entre les transferts des données et les calculs à effectuer. Le traitement représente moins de 10% du temps total, la majorité du temps étant réservé aux transferts des données dans le GPU.

Le temps d'exécution obtenu avec 2000 régions de taille 64x64 est d'environ 4 secondes, avec la récupération des copies mémoire et les traitements de données. Le goulot d'étranglement se fait sur le bus PCI-Express 2.0 avec 10 secondes de copies mémoire à la vitesse de 6 Go/s.

Figure 2-12: Pourcentage d'occupation du GPU entre le calcul et le transfert.

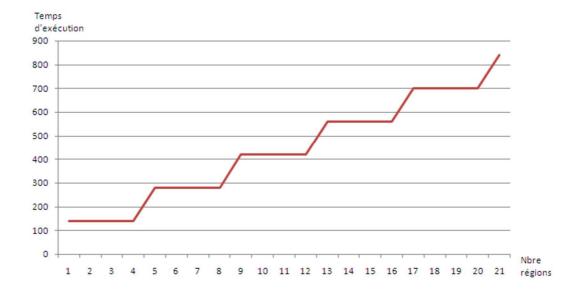

Les fonctions de calcul sont exécutées sur 4 MPs (32 processeurs) pour une région, et chaque processeur exécute séquentiellement 31 fois le même calcul. Le GPU ne peut exécuter que 4 régions au maximum en parallèle. Au-delà, la taille de la mémoire du GPU ne permet pas de stocker toutes les régions et il est nécessaire d'effectuer le calcul de manière séquentielle. Ainsi, le temps d'exécution augmente de 4 en 4 régions comme le montre la Figure 2-13.

Figure 2-13 : Calcul du temps d'exécution en fonction du nombre de régions (taille de fenêtre de 64\*64 pour 992 longueurs d'onde).